## FIGURES FOR CHAPTER 11

## LATCHES AND FLIP-FLOPS

#### This chapter in the book includes:

#### Objectives Study Guide

- 11.1 Introduction

- 11.2 Set-Reset Latch

- 11.3 Gated D Latch

- 11.4 Edge-Triggered D Flip-Flop

- 11.5 S-R Flip-Flop

- 11.6 J-K Flip-Flop

- 11.7 T Flip-Flop

- 11.8 Flip-Flops with Additional Inputs

- 11.9 Summary

- Problems

- Programmed Exercise

Click the mouse to move to the next page. Use the ESC key to exit this chapter.

Study Guide, No. 1

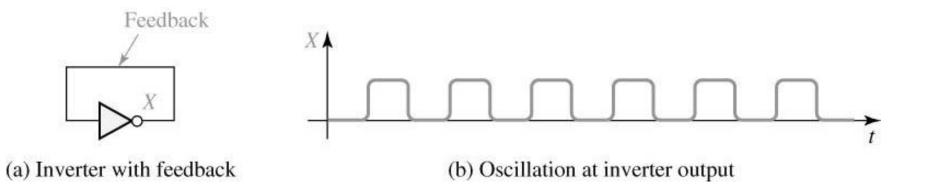

### Study Guide, No. 3c

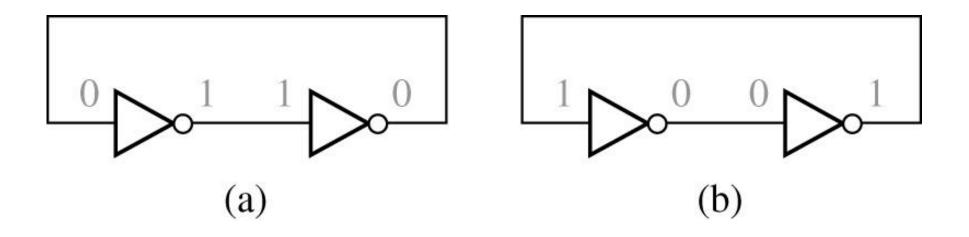

#### Study Guide, No. 4b

#### Study Guide, No. 4d

Study Guide, No. 7b

#### Study Guide, No. 8b

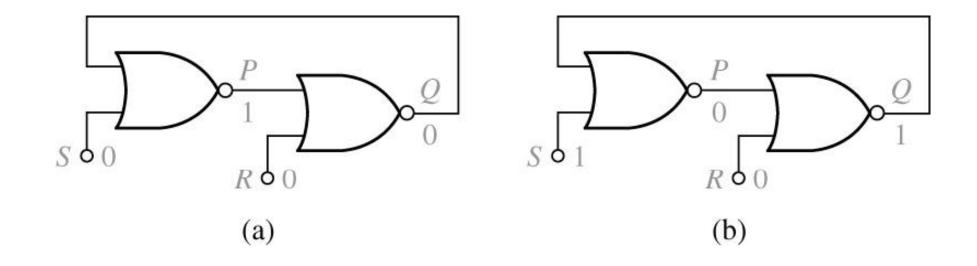

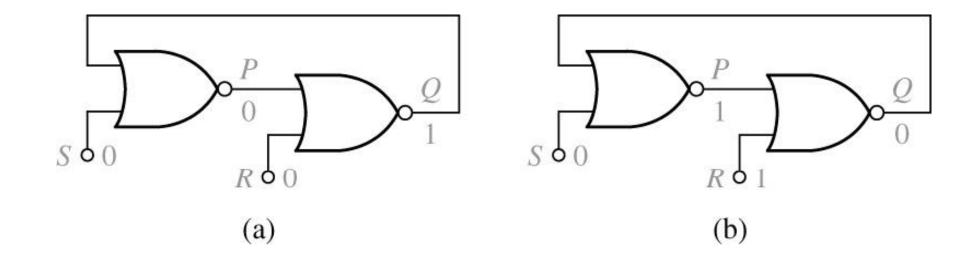

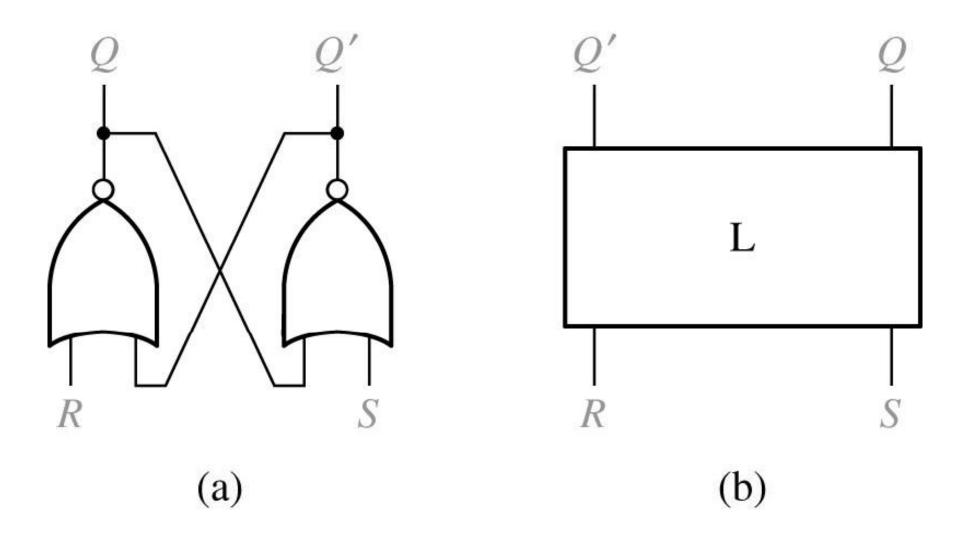

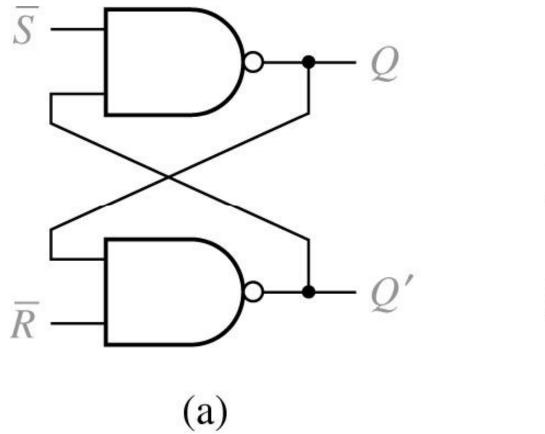

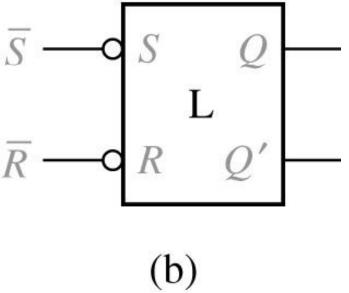

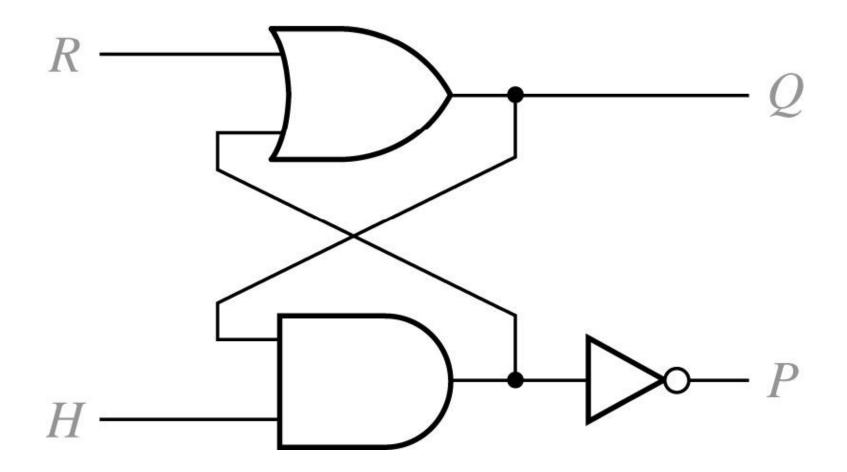

Figure 11-5: S-R Latch

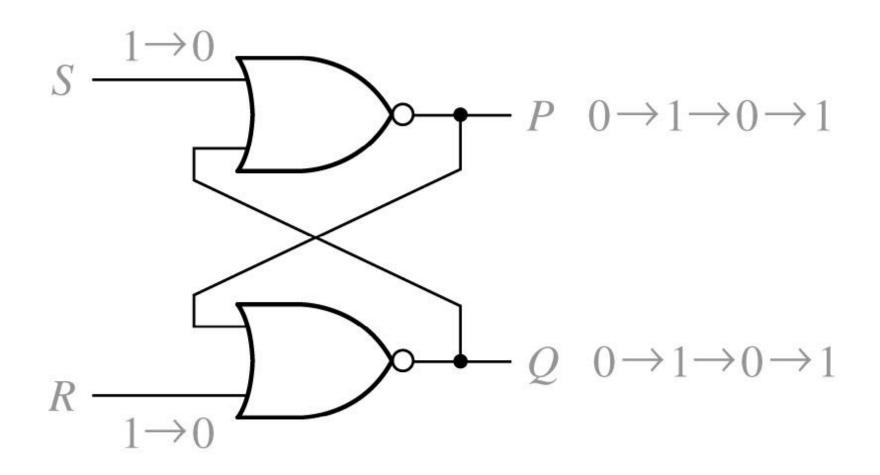

Figure 11-6: Improper S-R Latch Operation

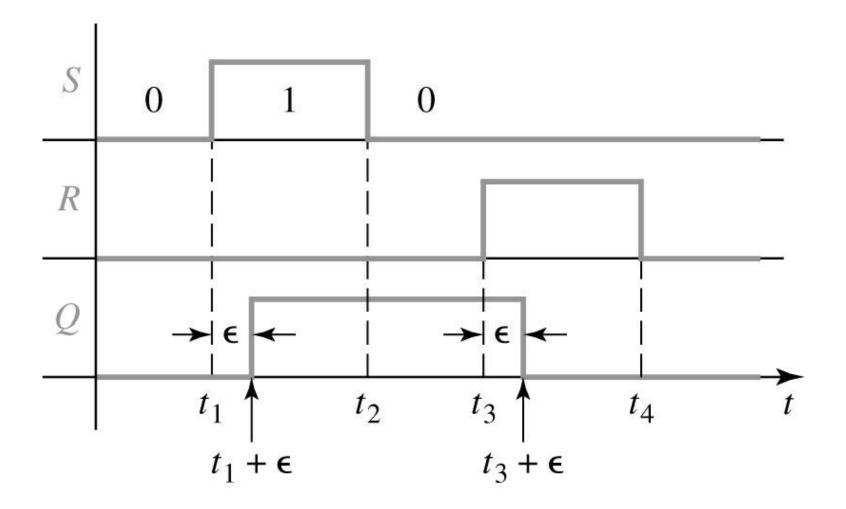

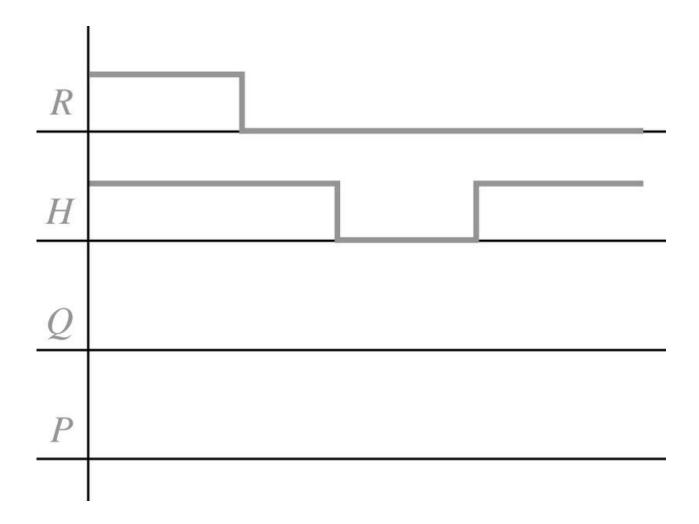

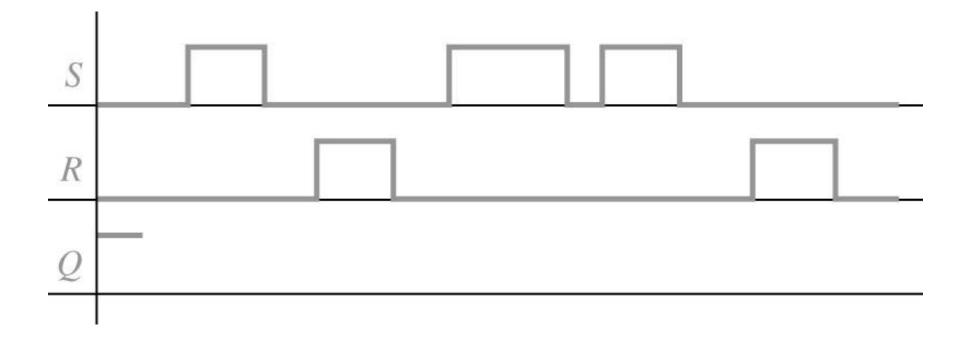

Figure 11-7: Timing Diagram for S-R Latch

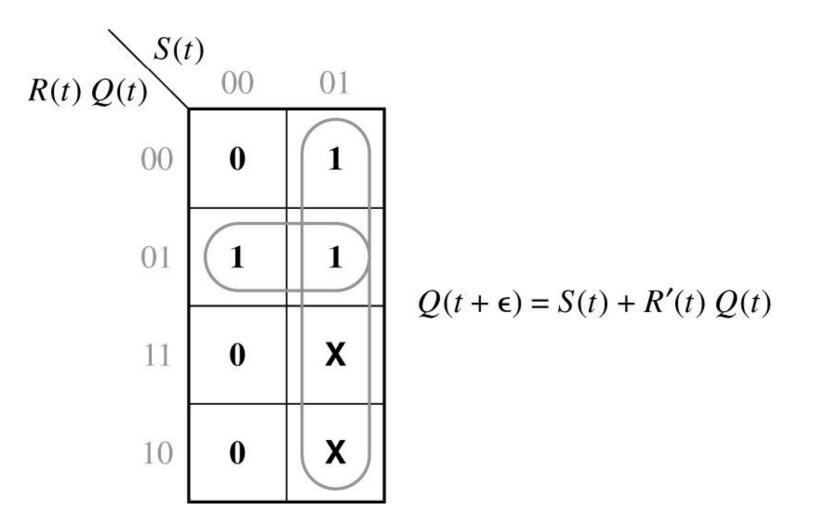

Figure 11-8: Map for Q(t + E)

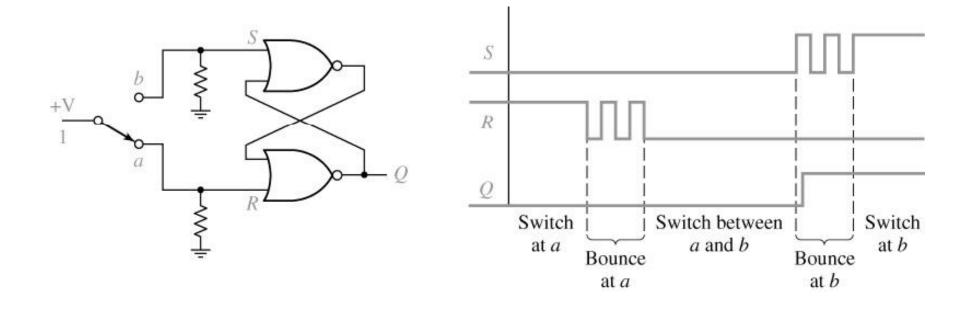

#### Figure 11-9: Switch Debouncing with an S-R Latch

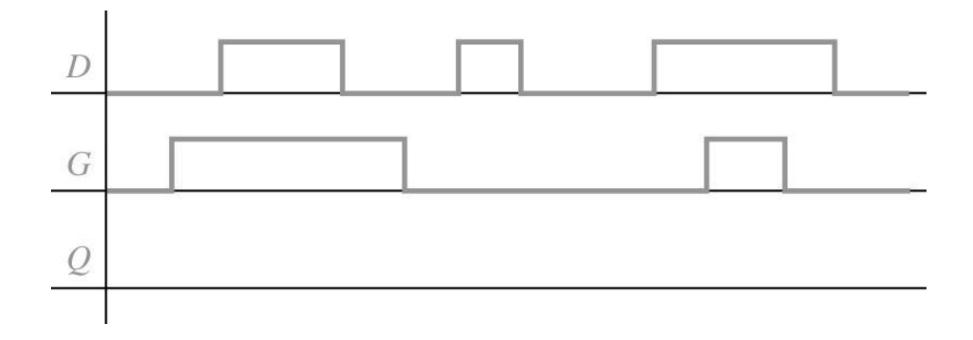

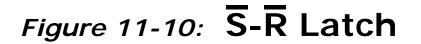

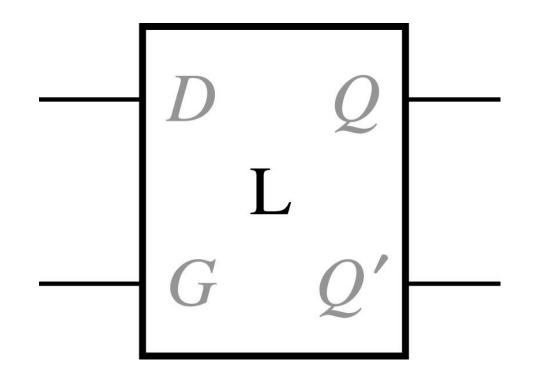

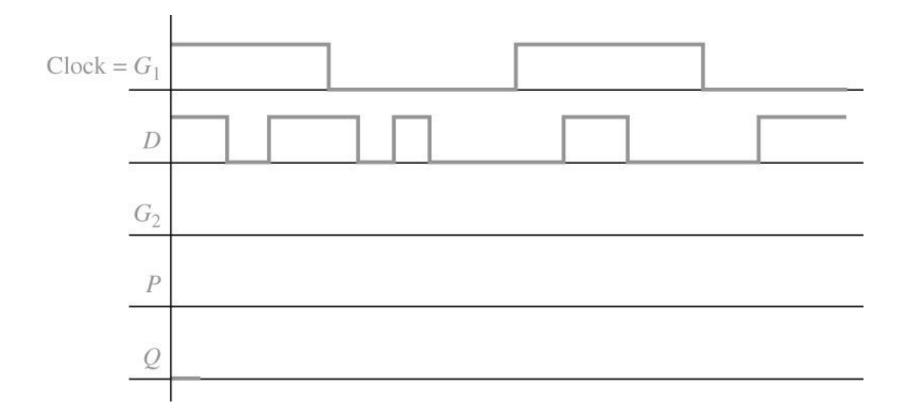

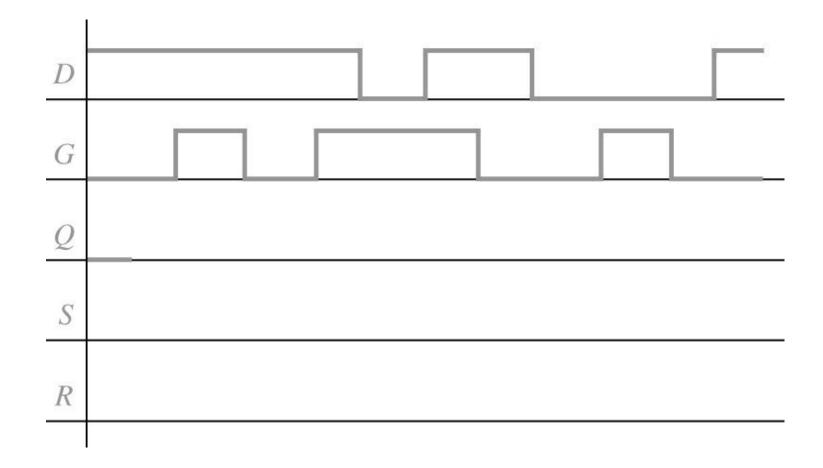

Figure 11-11: Gated D Latch

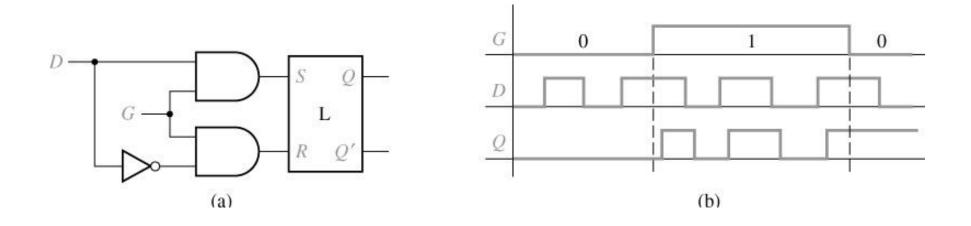

# Figure 11-12 (left): Symbol and Truth Table for Gated Latch

#### Figure 11-12 (right): Symbol and Truth Table for Gated Latch

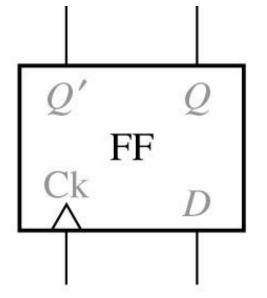

(a) Rising-edge trigger

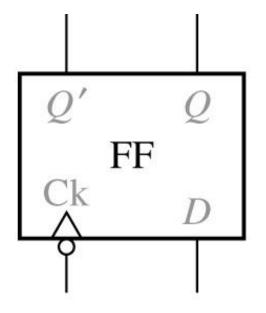

(b) Falling-edge trigger

#### Figure 11-13a and b: D Flip-Flops

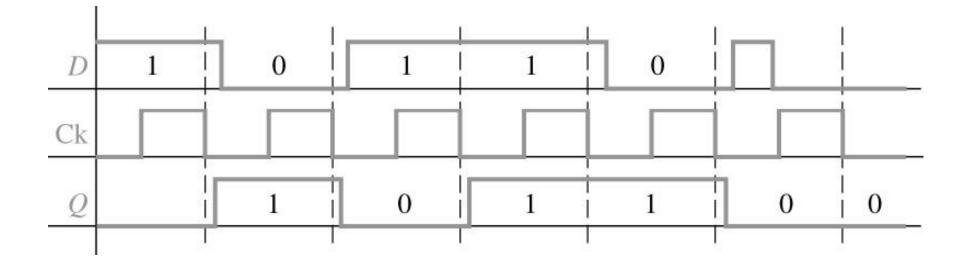

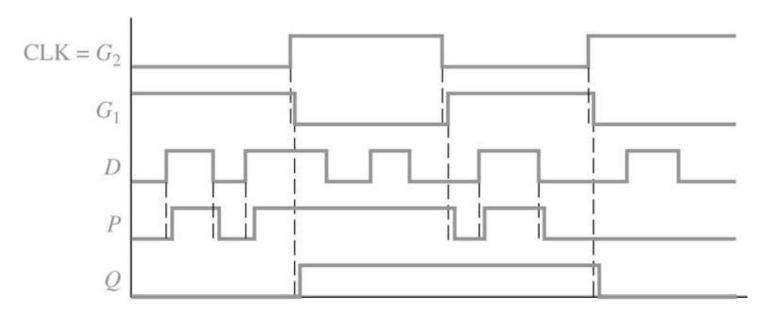

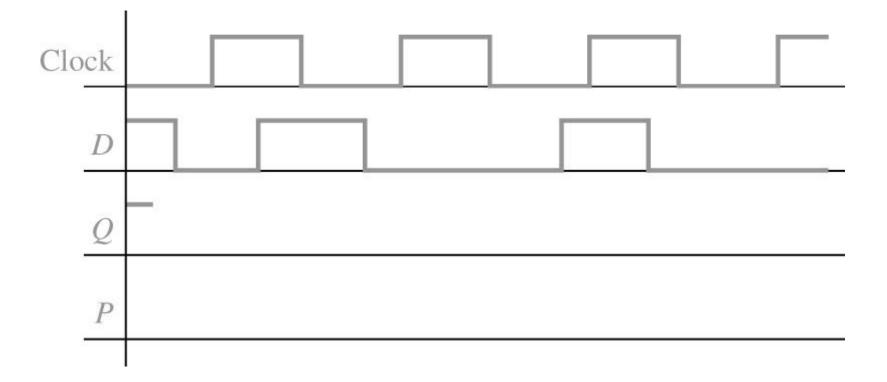

### Figure 11-14: Timing for D Flip-Flop (Falling Edge Trigger)

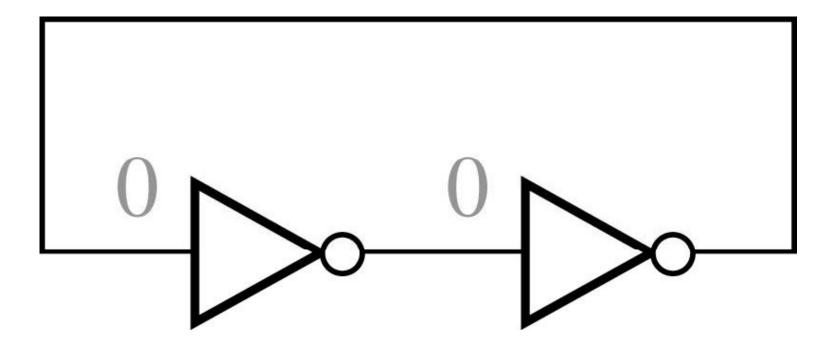

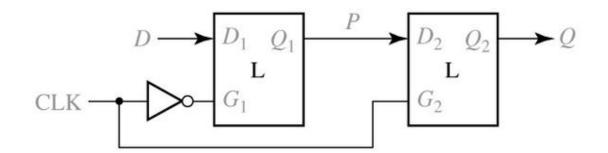

(a) Construction from two gated D latches

(b) Time analysis

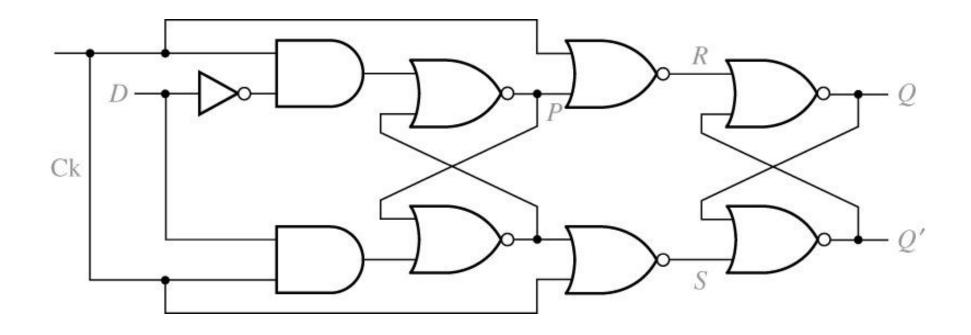

#### Figure 11-15: D Flip-Flop (Rising Edge Trigger)

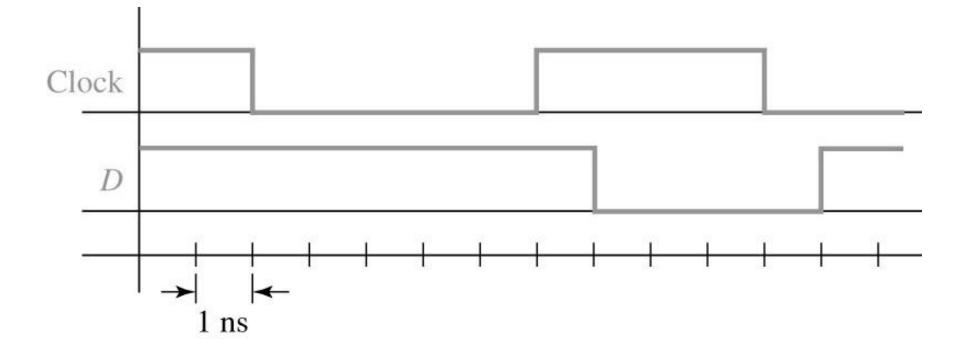

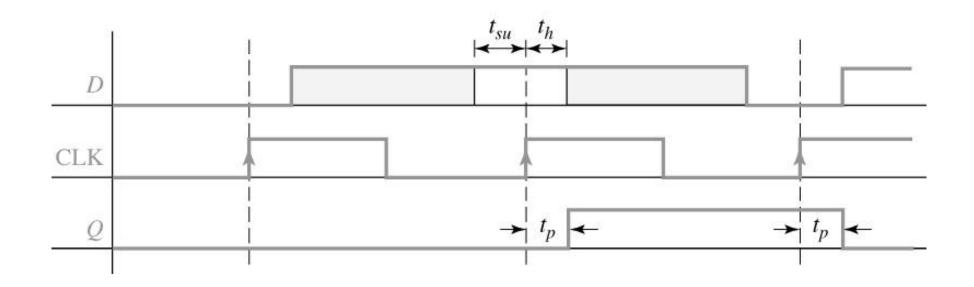

#### Figure 11-16: Setup and Hold Times for an Edge-Triggered D Flip-Flop

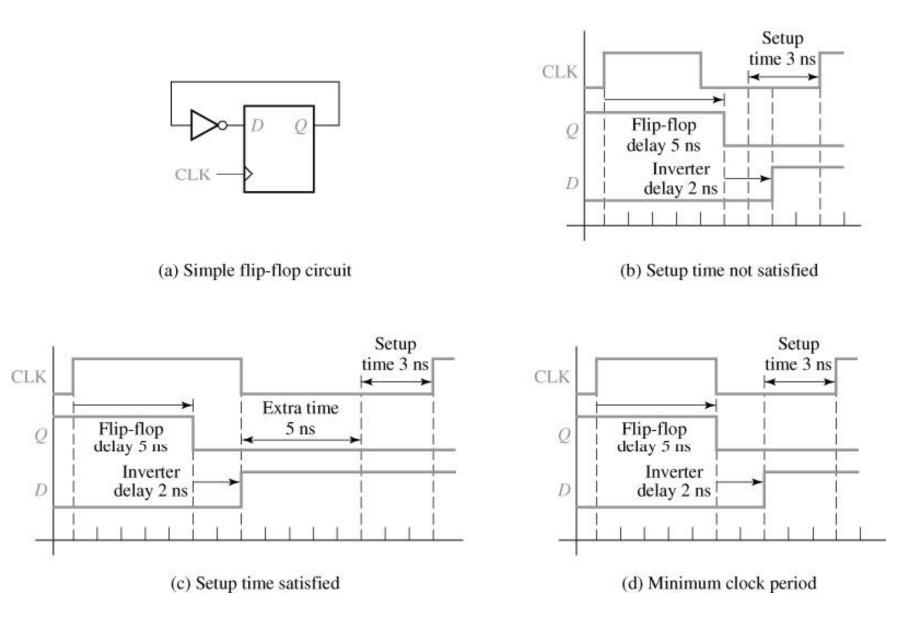

Figure 11-17: Determination of Minimum Clock Period

©2004 Brooks/Cole

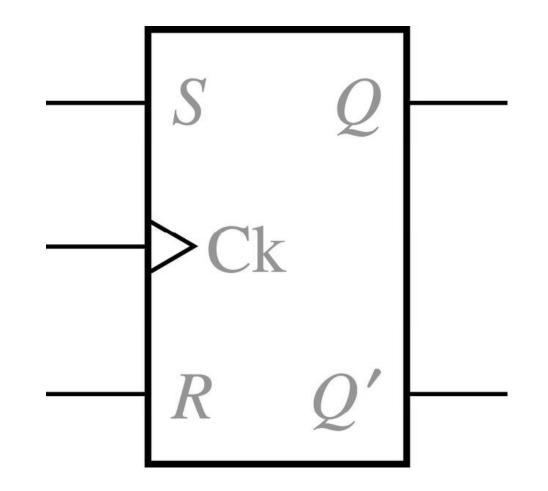

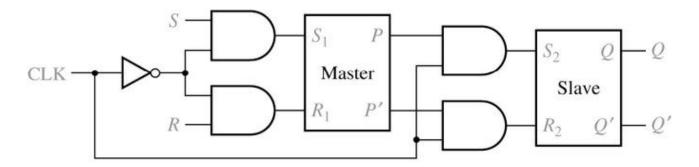

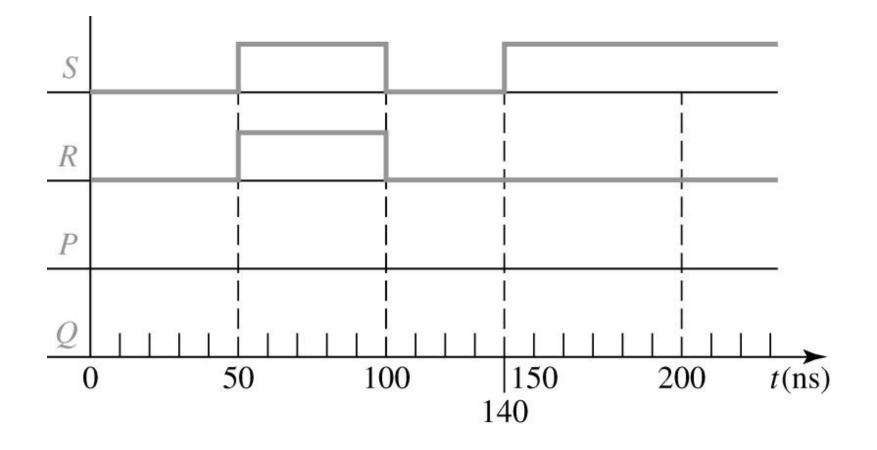

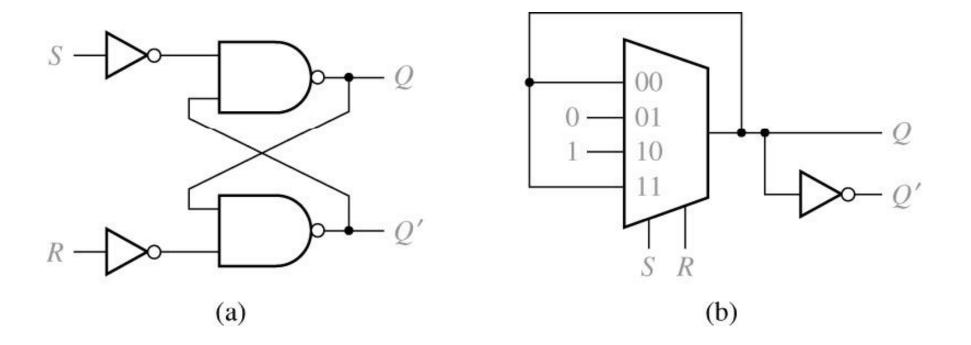

#### Figure 11-18: S-R Flip-Flop

(a) Implementation with two latches

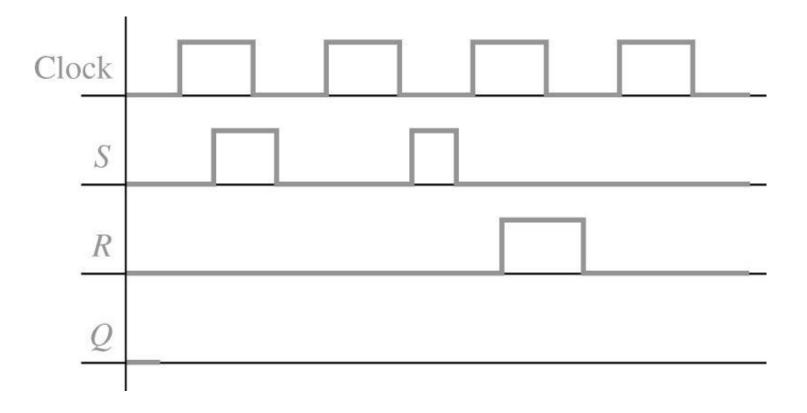

Figure 11-19: S-R Flip-Flop Implementation and Timing

©2004 Brooks/Cole

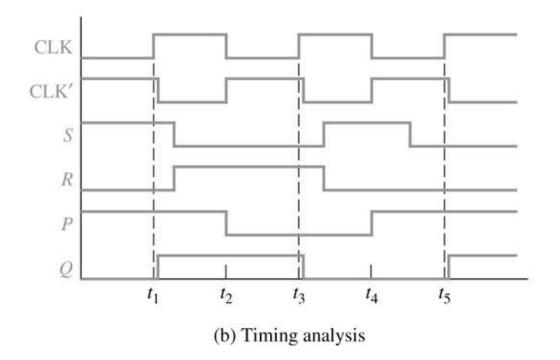

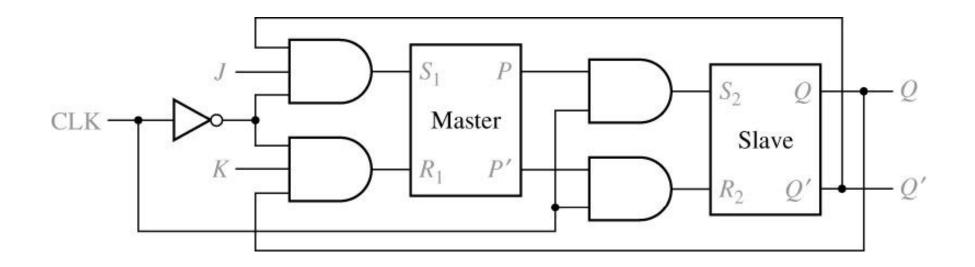

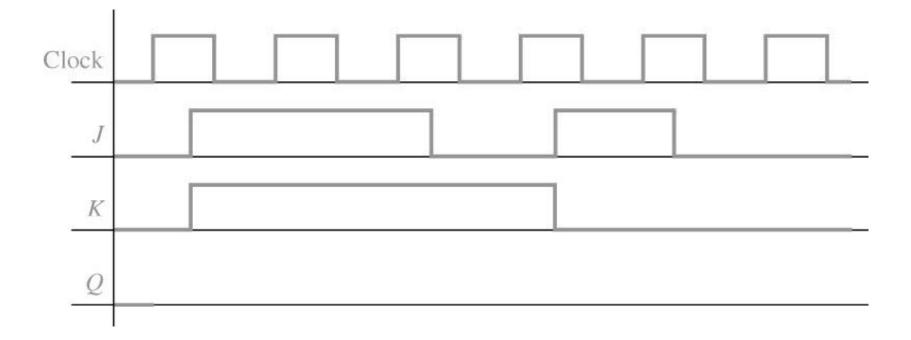

### (a) J-K flip-flop

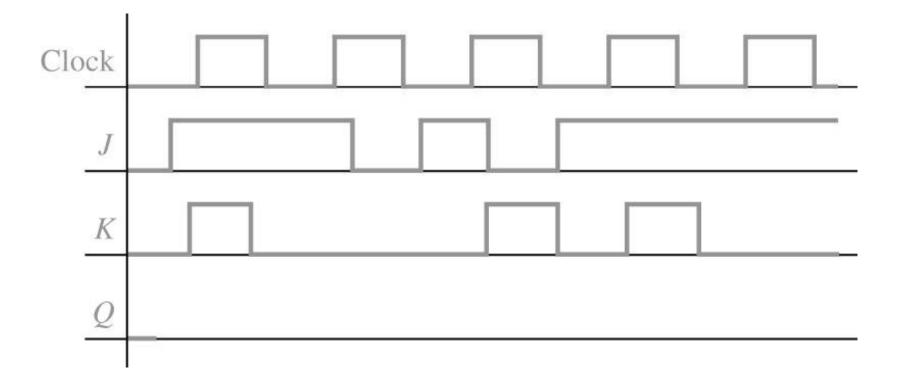

# *Figure 11-20a:* J-K Flip-Flop (*Q* Changes on the Rising Edge)

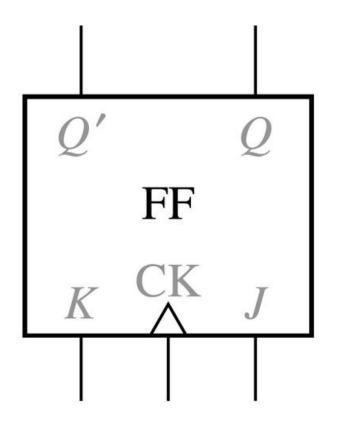

(c) J-K flip-flop timing

# *Figure 11-20c:* J-K Flip-Flop (*Q* Changes on the Rising Edge)

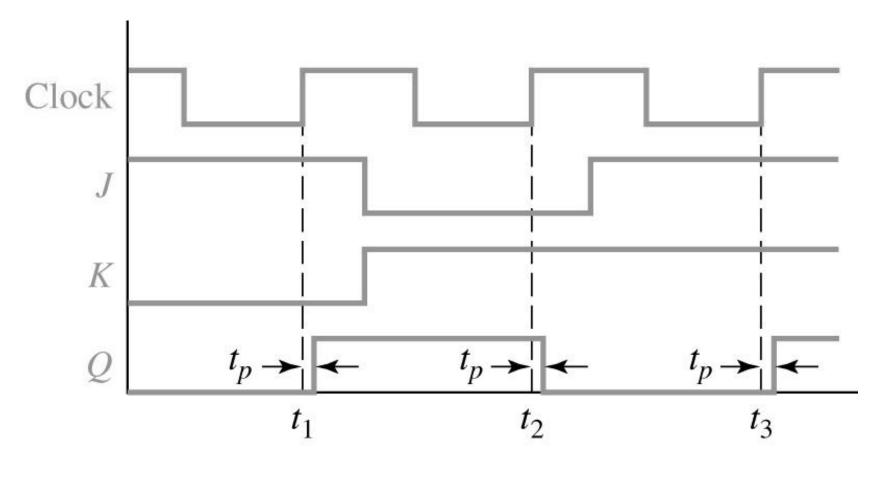

#### Figure 11-21: Master-Slave J-K Flip-Flop (*Q* Changes on Rising Edge)

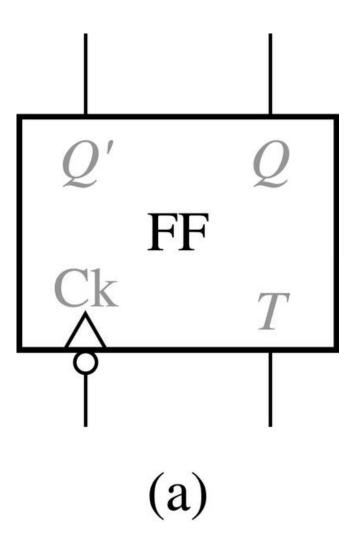

#### Figure 11-22a: T Flip-Flop

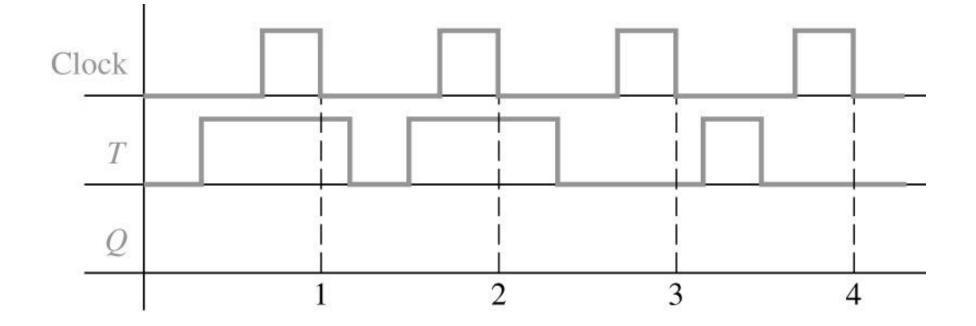

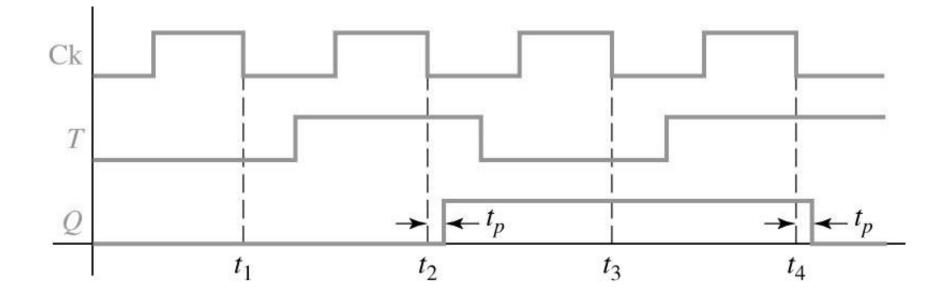

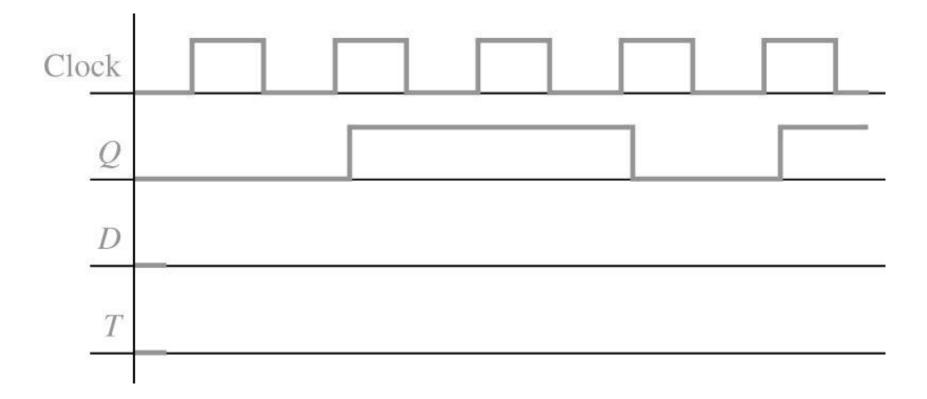

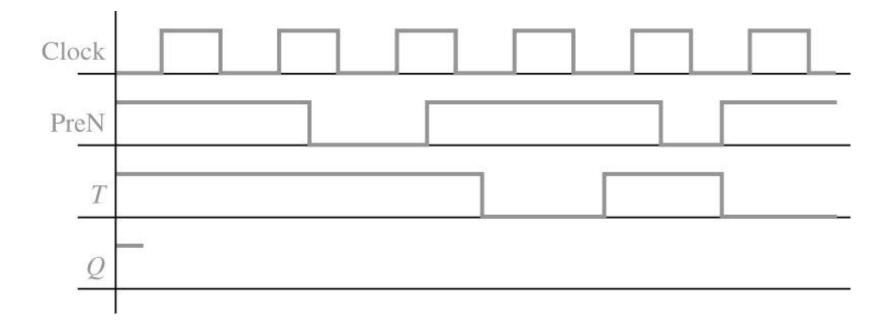

### Figure 11-23: Timing Diagram for T Flip-Flop (Falling-Edge Trigger)

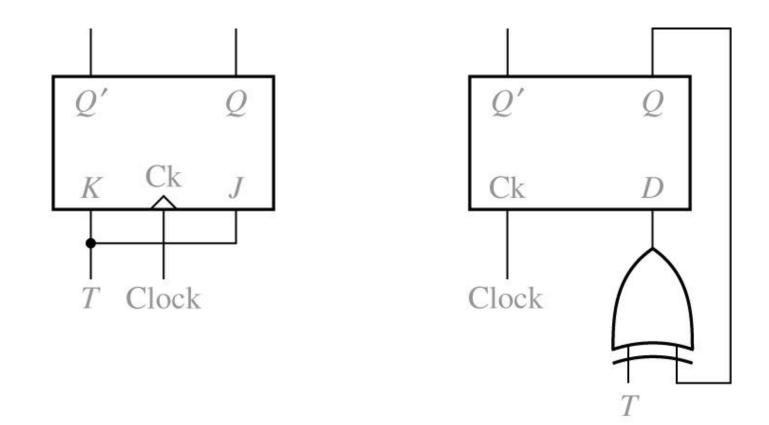

(a) Conversion of J-K to T

(b) Conversion of D to T

#### Figure 11-24: Implementation of T Flip-Flops

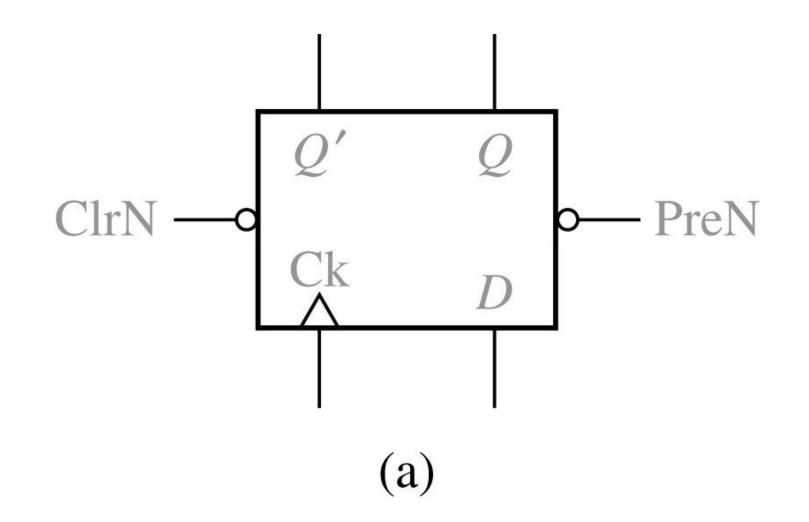

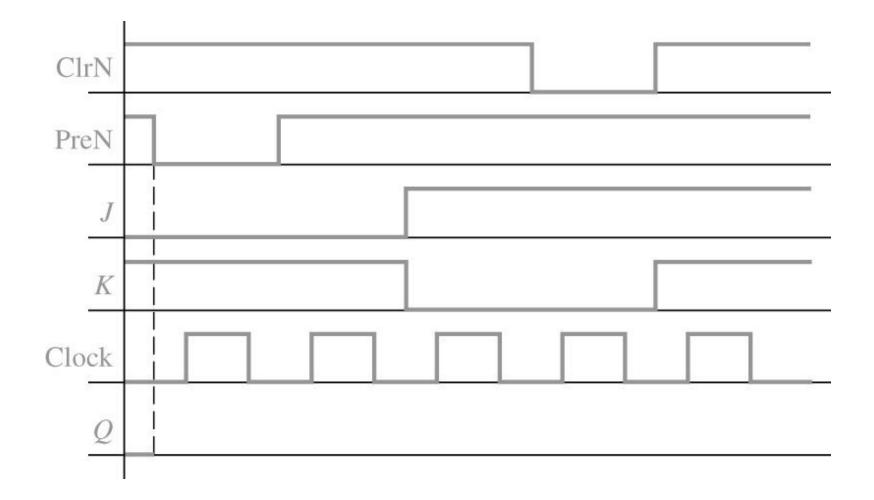

#### Figure 11-25: D Flip-Flop with Clear and Preset

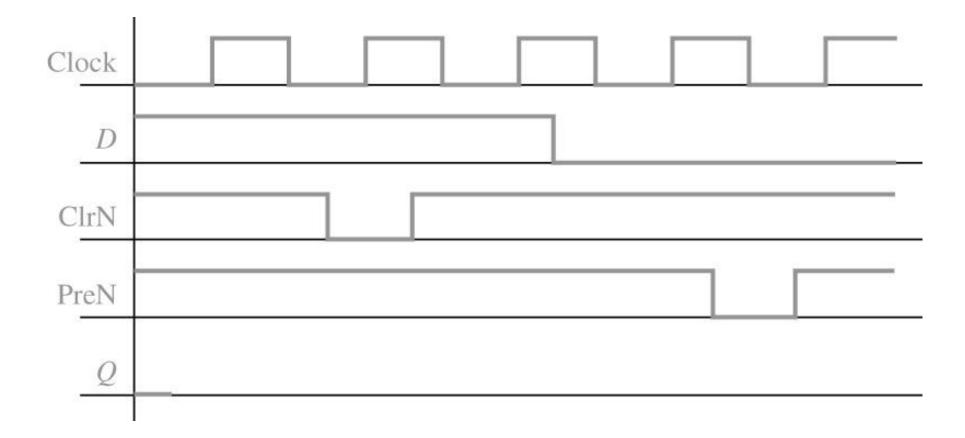

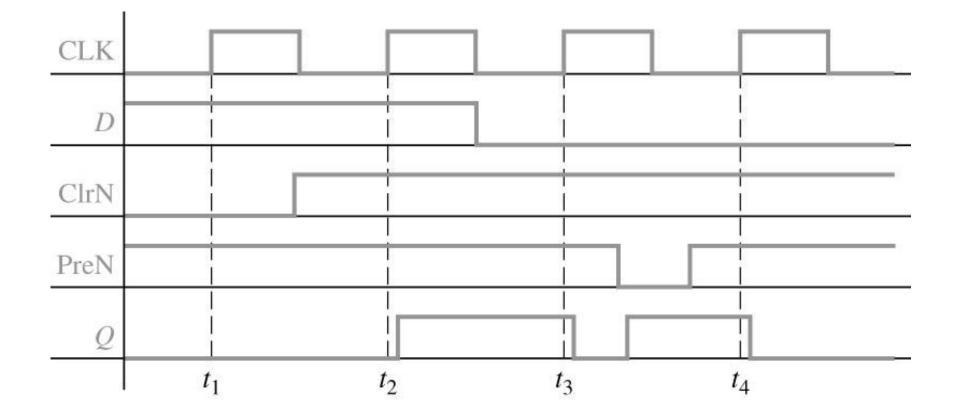

#### Figure 11-26: Timing Diagram for D Flip-Flop with Asynchronous Clear and Preset

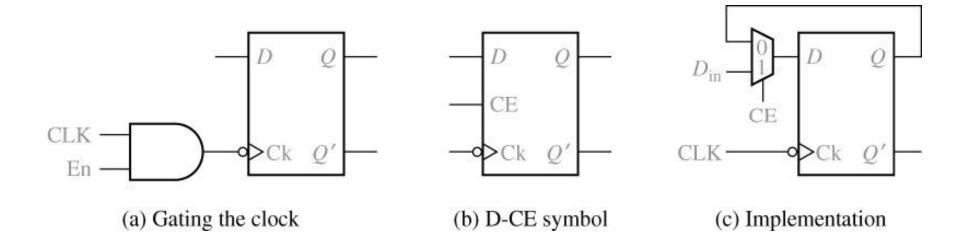

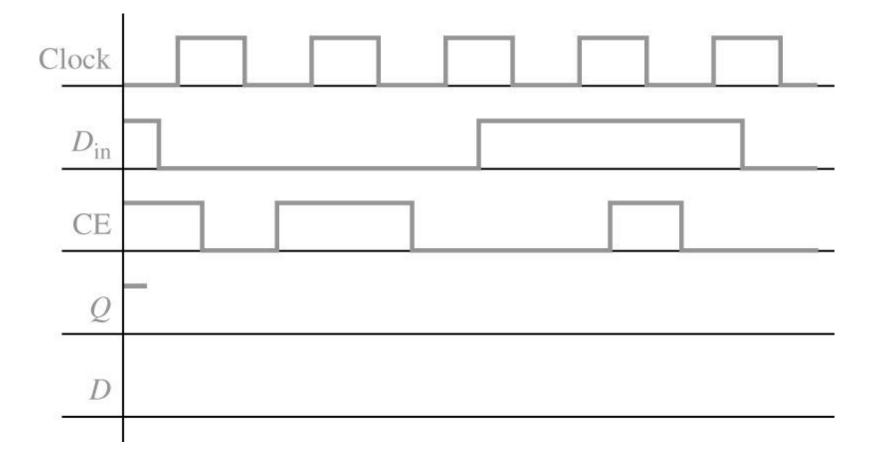

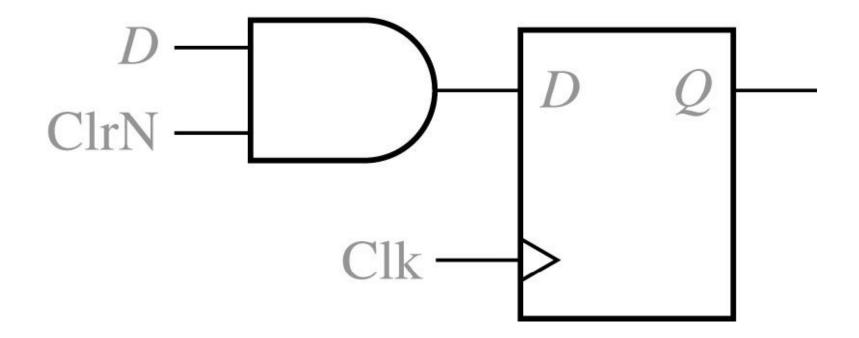

#### Figure 11-27: D Flip-Flop with Clock Enable

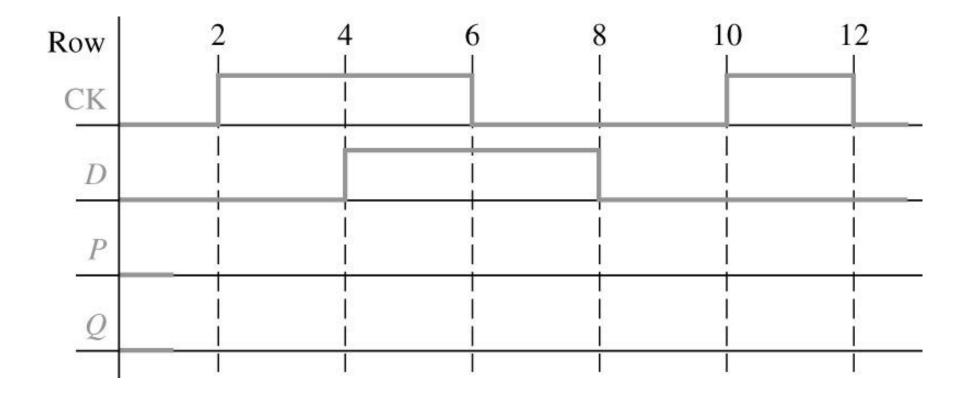

## Problem 11-21 (part 1)

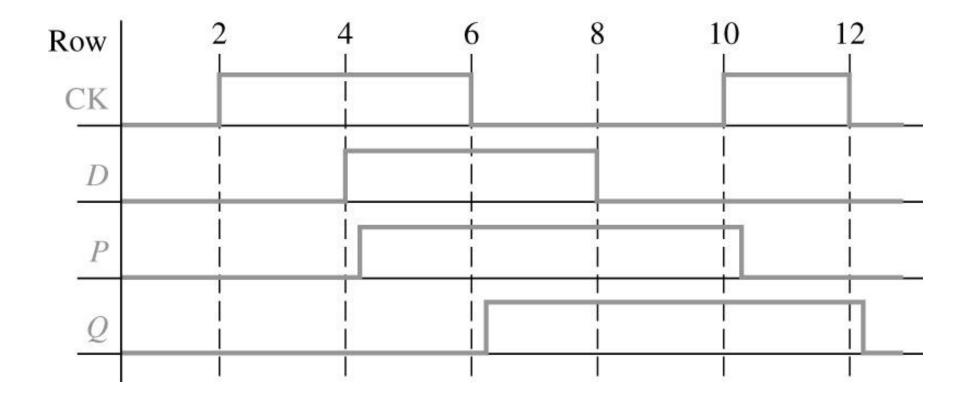

# Problem 11-21 (part 2)

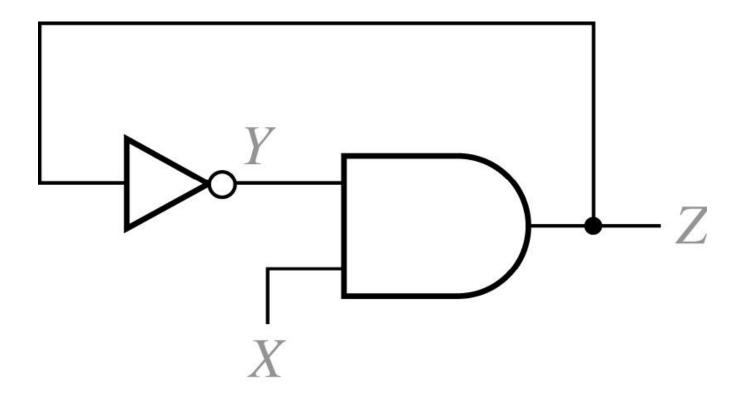

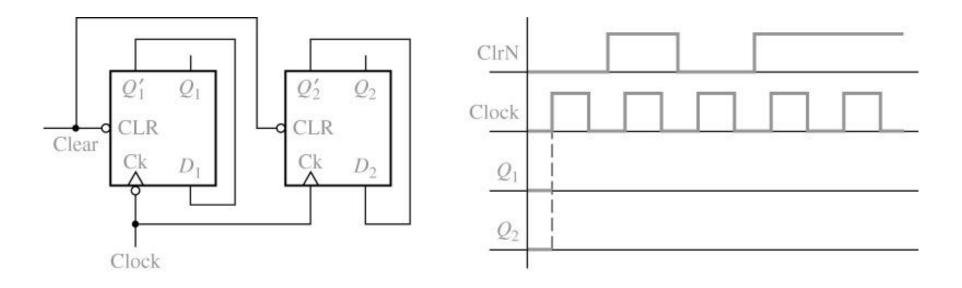

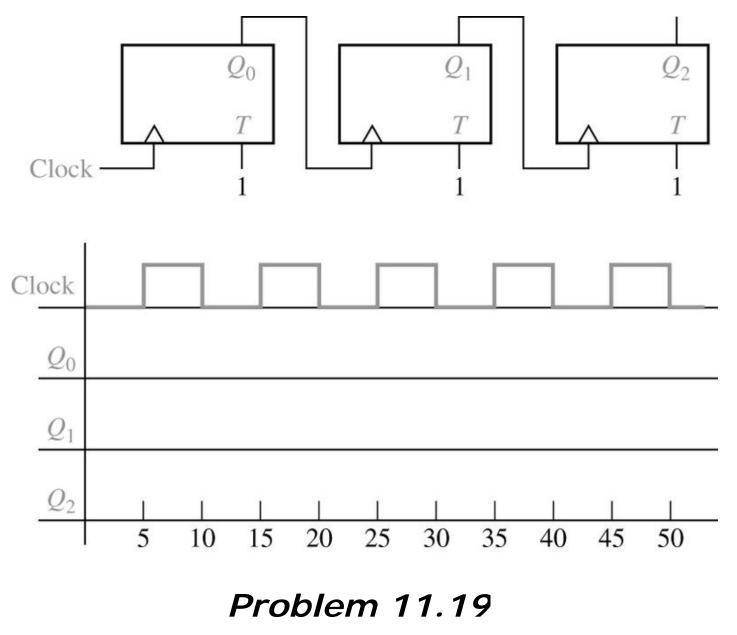

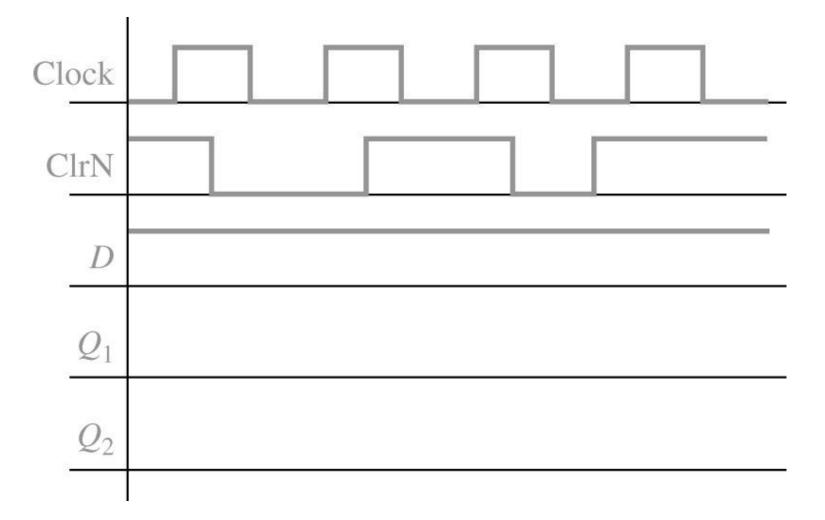

## Programmed Exercise 11.24 (diagram)

Programmed Exercise 11.24 (Answer 5 of 6)

Programmed Exercise 11.24 (Answer 6 of 6)